16年IC行業(yè)代理分銷(xiāo) 覆蓋全球300+品牌

現(xiàn)貨庫(kù)存,2小時(shí)發(fā)貨,提供寄樣和解決方案

24小時(shí)服務(wù)熱線(xiàn): 0755-82539998

現(xiàn)貨庫(kù)存,2小時(shí)發(fā)貨,提供寄樣和解決方案

熱搜關(guān)鍵詞:

在通信、儀器儀表和信號(hào)采集系統(tǒng)中,常常需要通過(guò)多個(gè)模數(shù)轉(zhuǎn)換器(ADC)同時(shí)對(duì)模擬輸入信號(hào)進(jìn)行采樣。由于各個(gè)輸入信號(hào)之間存在不同的延遲,因此必須對(duì)這些采樣的數(shù)據(jù)進(jìn)行同步處理。JESD204B標(biāo)準(zhǔn)為解決低電壓數(shù)字信號(hào)(LVDS)和并行輸出ADC之間的延遲不一致問(wèn)題提供了一種有效的解決方案。

JESD204B是一種用于傳輸高速串行數(shù)據(jù)的標(biāo)準(zhǔn)接口,特別適用于A(yíng)DC的輸出。它定義了如何利用一個(gè)或多個(gè)差分信號(hào)來(lái)發(fā)送數(shù)據(jù),并且支持通道間的粗調(diào)對(duì)齊。通過(guò)將數(shù)據(jù)分割成幀,并使用系統(tǒng)參考事件信號(hào)(SYSREF),JESD204B Subclass 1接口能夠確保多個(gè)串行通道鏈路或多個(gè)ADC的數(shù)據(jù)同步至SYSREF,從而實(shí)現(xiàn)發(fā)射器和接收器內(nèi)部幀時(shí)鐘的同步化。這保證了設(shè)備間具有確定性的延遲,但要達(dá)到徹底的時(shí)序收斂,還需要克服一些挑戰(zhàn),包括PCB布局、時(shí)鐘匹配以及SYSREF生成等。

時(shí)鐘與SYSREF生成:設(shè)計(jì)師需決定設(shè)備時(shí)鐘和SYSREF信號(hào)的生成方式及其在系統(tǒng)中的分配策略。理想情況下,兩者應(yīng)具有相同的擺幅和電平偏移,以避免引入額外的固有時(shí)延。

SYSREF的應(yīng)用模式:可以作為單次觸發(fā)或重復(fù)信號(hào)使用,取決于系統(tǒng)的具體需求。無(wú)論是哪種模式,都需要仔細(xì)規(guī)劃PCB布局,確保滿(mǎn)足建立和保持時(shí)間的要求。

FPGA的角色:雖然FPGA可以用來(lái)生成SYSREF事件,但如果FPGA未與主時(shí)鐘同步,則難以實(shí)現(xiàn)SYSREF與主時(shí)鐘的相位對(duì)齊。更優(yōu)的選擇是由時(shí)鐘發(fā)生或分配芯片提供SYSREF信號(hào),這樣可以更容易地實(shí)現(xiàn)多時(shí)鐘同步。

為了初始化ADC通道的確定起始點(diǎn),系統(tǒng)工程師必須滿(mǎn)足所有分布在系統(tǒng)中的SYSREF的時(shí)序要求。這意味著不僅要考慮時(shí)鐘相關(guān)的建立和保持時(shí)間,還需特別注意PCB布局,確保時(shí)鐘和SYSREF布線(xiàn)長(zhǎng)度匹配,盡量減少偏斜。隨著ADC編碼時(shí)鐘速率的增加及系統(tǒng)復(fù)雜度的提升,這一過(guò)程變得更加困難。

此外,系統(tǒng)工程師還需要識(shí)別每個(gè)器件上的SYSREF至?xí)r鐘的偏斜,并在FPGA或ASIC內(nèi)有效地歸零任何殘余的數(shù)字和時(shí)鐘偏斜延遲。后臺(tái)處理可以通過(guò)調(diào)整ADC的采樣順序來(lái)進(jìn)行必要的重對(duì)齊,以便為后續(xù)的數(shù)據(jù)同步處理做準(zhǔn)備。

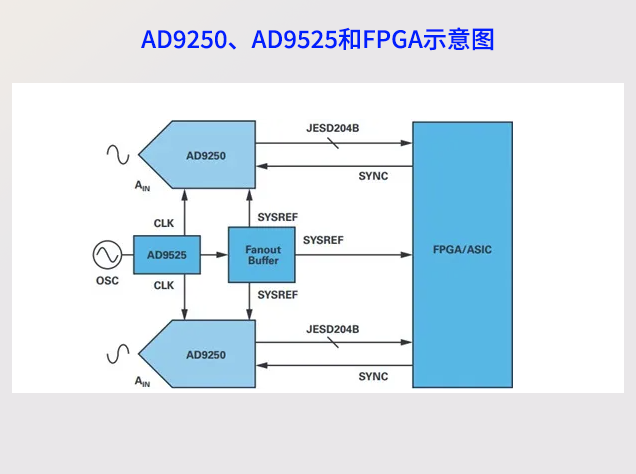

AD9250是一款由ADI公司提供的250 MSPS、14位雙通道ADC,支持JESD204B接口的subclass 1實(shí)施,可用于實(shí)現(xiàn)ADC采樣同步。搭配AD9525這款低抖動(dòng)時(shí)鐘發(fā)生器,不僅能提供高達(dá)3.1 GHz的7個(gè)時(shí)鐘輸出,還能根據(jù)用戶(hù)配置同步SYSREF輸出信號(hào)。結(jié)合ADI的扇出緩沖器產(chǎn)品系列,可以精確地同步與對(duì)齊多個(gè)ADC的數(shù)據(jù),使其順利發(fā)送至FPGA或ASIC進(jìn)行處理。如需AD9250產(chǎn)品規(guī)格書(shū)、樣片測(cè)試、采購(gòu)、BOM配單等需求,請(qǐng)加客服微信:13310830171。

總之,通過(guò)合理的設(shè)計(jì)選擇與時(shí)鐘管理,利用JESD204B標(biāo)準(zhǔn),工程師們可以構(gòu)建出高效、可靠的多ADC同步系統(tǒng),顯著提高系統(tǒng)的整體性能和穩(wěn)定性。這對(duì)于追求高精度、實(shí)時(shí)性要求嚴(yán)格的現(xiàn)代電子系統(tǒng)尤為重要。