13年IC行業(yè)代理分銷(xiāo) 覆蓋全球300+品牌

現(xiàn)貨庫(kù)存,2小時(shí)發(fā)貨,提供寄樣和解決方案

24小時(shí)服務(wù)熱線: 0755-82539998

現(xiàn)貨庫(kù)存,2小時(shí)發(fā)貨,提供寄樣和解決方案

熱搜關(guān)鍵詞:

比利時(shí)微電子研究中心(imec)在2024年IEEE超大規(guī)模集成電路技術(shù)研討會(huì)(2024 VLSI)上首次展示了具有堆疊底部和頂部源極/漏極電功能的CMOS CFET互補(bǔ)場(chǎng)效應(yīng)管元件。這一成果以創(chuàng)新的技術(shù)實(shí)現(xiàn),提升了頂部元件的覆蓋率,展望引入CFET晶體管技術(shù)在未來(lái)A7節(jié)點(diǎn)(0.7nm)可能帶來(lái)的潛在影響。

imec邏輯芯片技術(shù)路線圖顯示,未來(lái)將在A7節(jié)點(diǎn)(0.7nm)引入CFET晶體管技術(shù)。結(jié)合先進(jìn)的布線技術(shù),CFET有望在不降低性能的情況下,將標(biāo)準(zhǔn)單元走線高度從5T降低至4T甚至更低。而在集成nMOS和pMOS垂直堆疊結(jié)構(gòu)的不同方法中,單片集成被認(rèn)為是與現(xiàn)有納米片工藝流程相比,破壞性最小的方法。

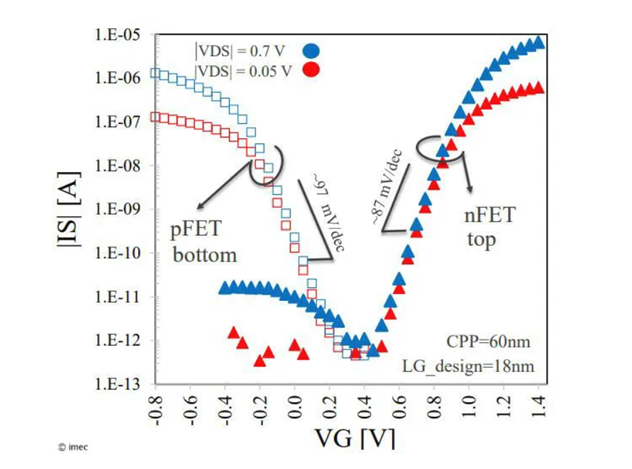

imec的實(shí)驗(yàn)展示了具有頂部和底部堆疊觸點(diǎn)的功能性單片CMOS CFET器件,柵極長(zhǎng)度為18nm,柵極間距為60nm,n型半導(dǎo)體和p型半導(dǎo)體之間的垂直間隔為50nm。測(cè)試晶圓上的nFET和pFET使用一個(gè)公共柵極,頂部和底部觸點(diǎn)從正面連接。

確切的工藝流程包括兩個(gè)關(guān)鍵的CFET特定模塊:中間電介質(zhì)隔離(MDI),以及堆疊的底部和頂部相互接觸。據(jù)官方介紹,MDI是imec首創(chuàng)的模塊結(jié)構(gòu),用于隔離頂部和底部的柵極,并區(qū)分n和p型半導(dǎo)體的閾值電壓。另一個(gè)關(guān)鍵模塊結(jié)構(gòu)是堆疊源極/漏極底部和頂部的觸點(diǎn),需要通過(guò)電介質(zhì)垂直隔離,并應(yīng)用底部觸點(diǎn)的金屬填充和回蝕,以及隨后步驟的電介質(zhì)填充和回蝕。

imec負(fù)責(zé)人表示,在開(kāi)發(fā)基于正面開(kāi)始加工的底部接觸結(jié)構(gòu)時(shí),遇到了很多挑戰(zhàn),可能影響底部接觸電阻,并限制頂部器件工藝窗口。然而,在2024年VLSI上,該機(jī)構(gòu)證實(shí)了這一設(shè)計(jì)的可行性,并指出這使得晶圓背面底部接觸結(jié)構(gòu)成為對(duì)業(yè)界具有強(qiáng)大吸引力的選擇。目前,imec正在進(jìn)行進(jìn)一步研究,以確定最佳的觸點(diǎn)布線方法。